时间:2024-07-11

时间:2024-07-11  来源:SJK

来源:SJK

上篇我们对有源晶振信号的输出种类做了个简单的分析,那么选择哪种信号类型取决于应用的具体需求,接下来,让我们来详细来了解每种输出信号的类型,以更好地了解它们的优点和用途。这将使您更清楚地了解哪种类型最适合您的需求。

单端:正弦波和削波正弦波(Sinewave & Clipped Sinewave)

这是晶体振荡器电路的标准或“原始”信号输出。它仅由一个基频组成,不存在任何谐波。这将提供振荡器可以预期的最大频谱波动。正弦波输出非常适合要求苛刻的低相位噪声应用。

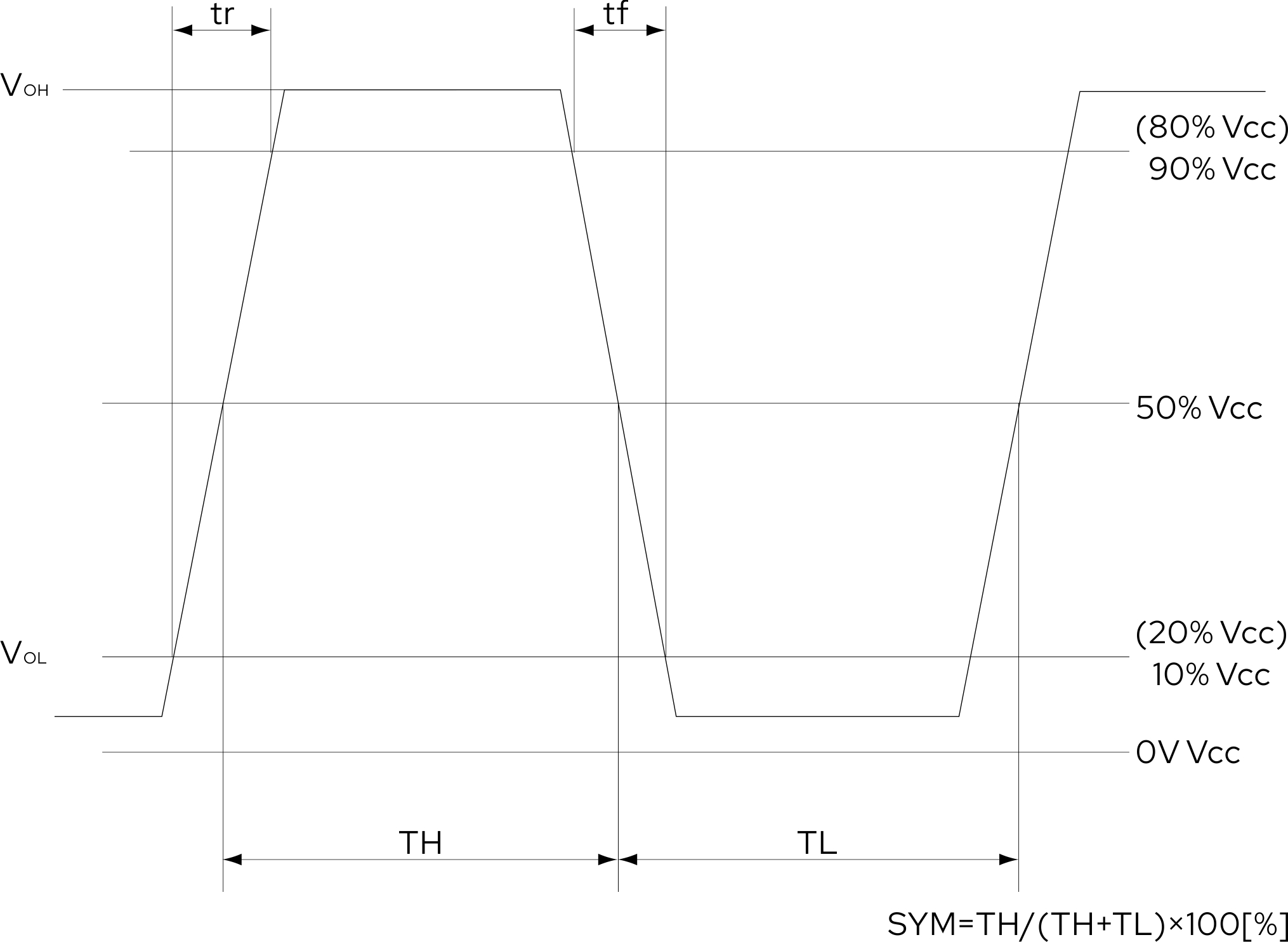

单端:互补金属氧化物半导体(CMOS: Complementary Metal Oxide Semiconductor)、HCMO和LVCMOS

互补金属氧化物半导体(CMOS)输出适用于较短的走线长度和较低频率的时钟源(低于 220MHz)。这将允许时钟输出和接收器输入之间直接连接。在大多数情况下,可以使用低值串联电阻器来有效减少反射并保持可靠的信号。此外,还有高速(HCMOS)和低压(LVCMOS) 输出,可能更适合您的特定需求。

CMOS信号输出波形

单端:晶体管到晶体管逻辑(TTL: Transistor-to-Transistor Logic)

在大多数情况下,TTL已经被CMOS淘汰了。这是因为CMOS比TTL具有更低的成本和更好的抗噪性。CMOS和TTL都非常适合低功耗、高输出摆幅和相对较低的成本需求。

差分:发射极耦合逻辑(ECL: Emitter Coupled Logic)

ECL 主要是作为 TTL 的良好替代品引入的。ECL电路可以非常快速地改变状态,这使得它们更能满足非常高速的数据传输需求。然而,ECL确实有一些缺点。它需要相当高的电流才能运行,并使用负电源,这在尝试连接到正极基极电源设备时可能会带来挑战。

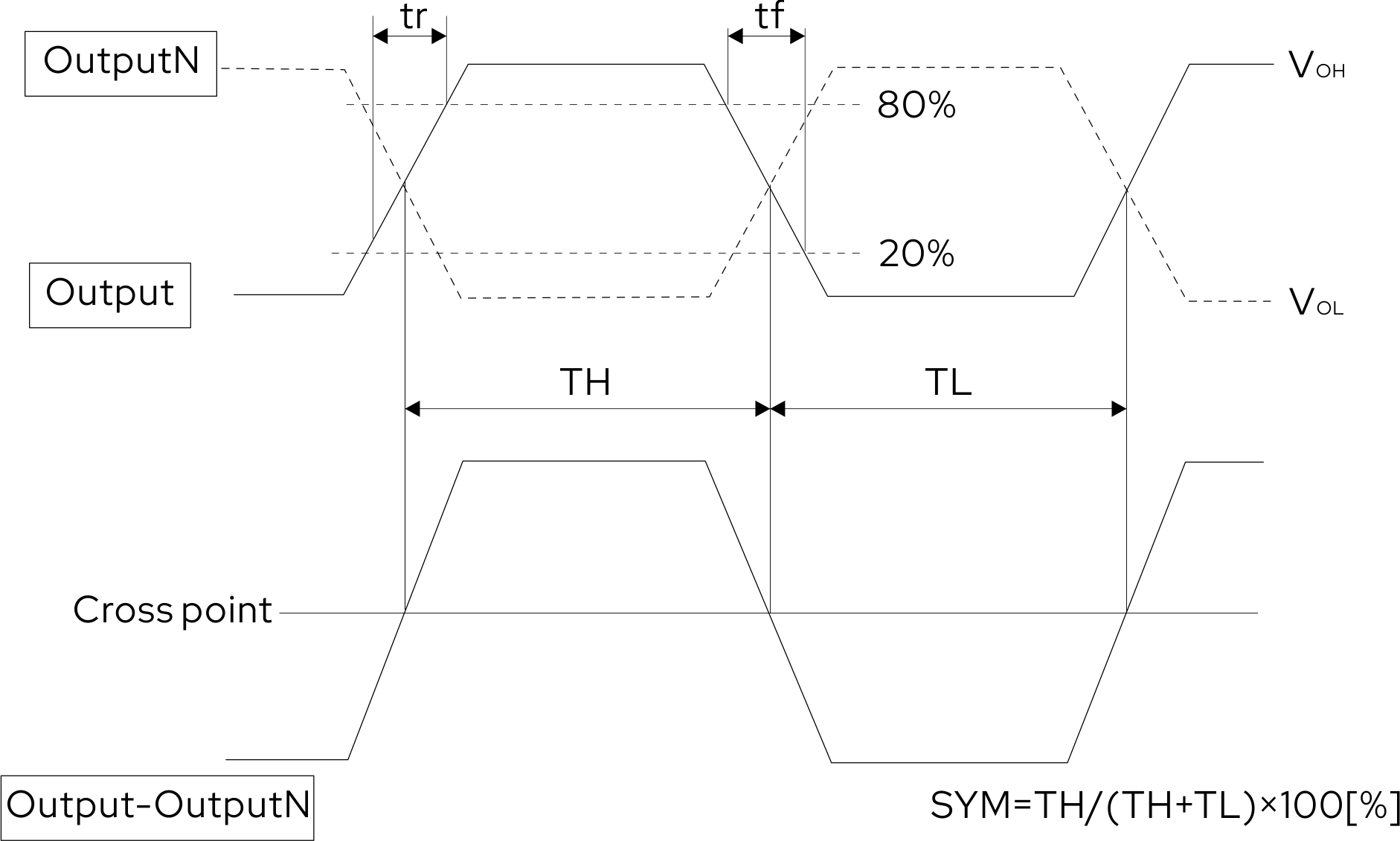

差分:正发射极耦合逻辑(PECL: Positive Emitter Coupled Logic)和LVPECL

正发射极耦合逻辑(PECL)输出经常用于高速时钟分配电路。这是因为PECL具有高抗噪性、在长线路长度上驱动高数据速率的能力,以及由于电压摆幅大而具有的良好抖动性能。PECL的主要缺点是需要高功耗才能运行。

低压PECL(LVPECL)为千兆以太网(GbE)和光纤通道的使用奠定了良好的基础。LVPECL在电气上与低压差分信号(LVDS)相似,但提供更大的差分电压摆幅和略低的电源效率。LVPECL的输出可能会出现一些挑战,因为需要端接来发射电压。另请注意,不同制造商的差分接收器可能具有不同的输入容差。所以,请一定记住你所需要的规格,了解哪种接收器最适合您!

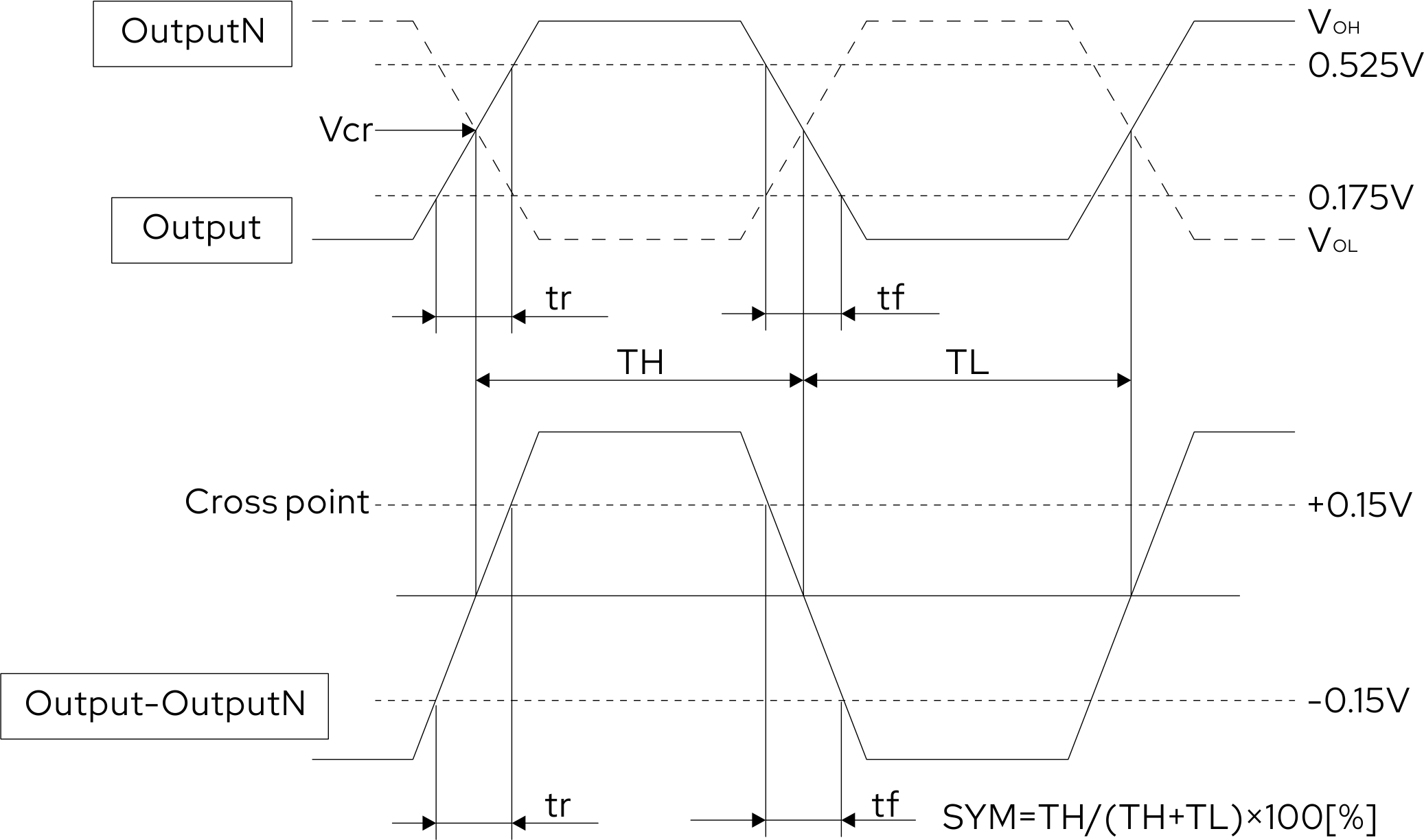

LVPECL信号输出波形

差分:电流模式逻辑(CML:Current-Mode Logic)

CML具有与LVPECL相似的性能。主要区别在于CML不需要外部偏置。这使得CML在低功耗问题时成为LVPECL的良好替代品。

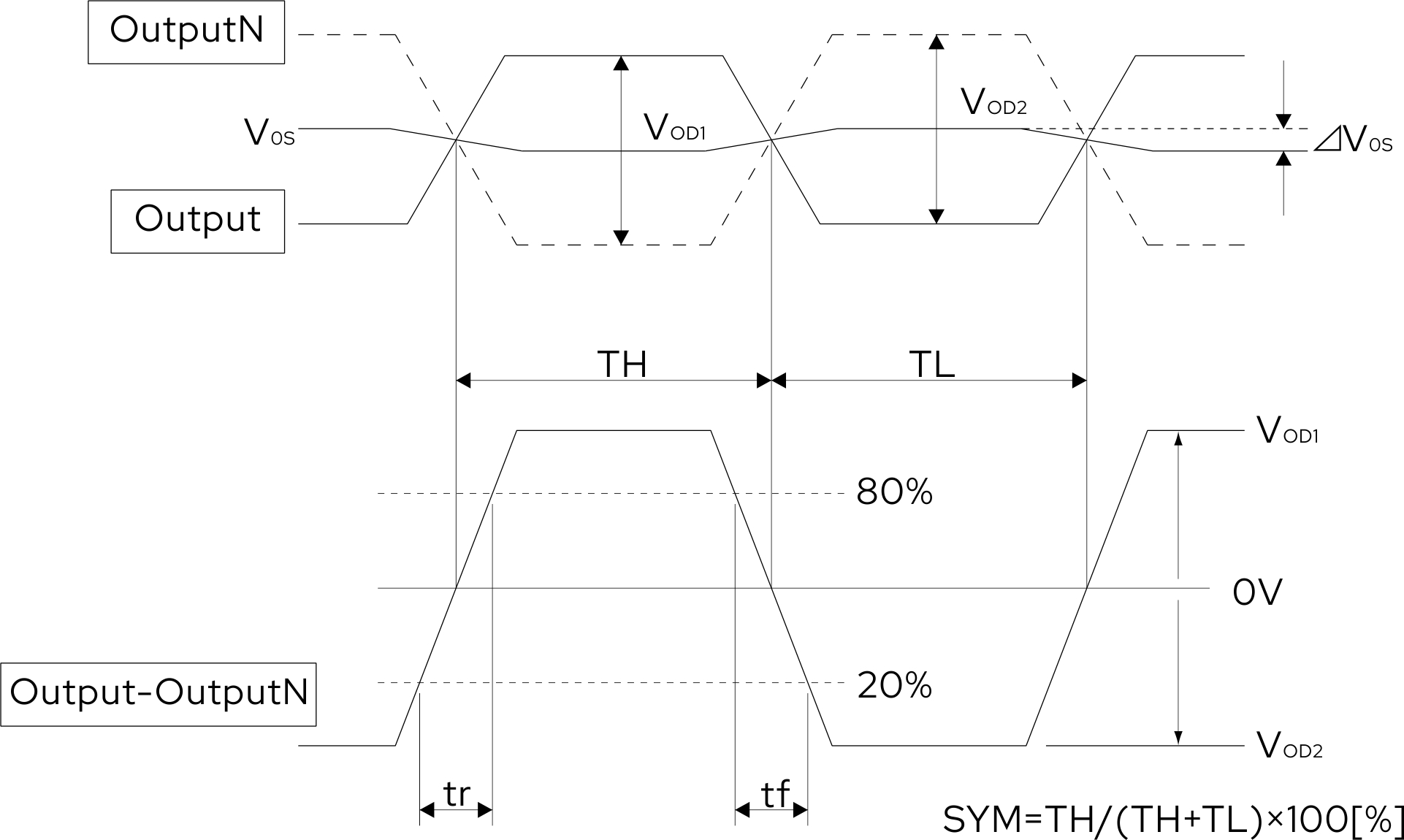

差分:低压差分信号(LVDS:Low Voltage Differential Signaling)

LVDS与LVPECL类似,但LVDS的功耗较低,电压摆幅往往较小。此输出通常用于高速数据传输需求,如时钟分配或背板收发器。对于更高的数据速率,通常需要高速电流转向逻辑 (HCSL)、CML 或 LVPECL,但需要比 LVDS 更高的功耗。

LVDS还降低了对噪声的敏感性,并且易于在CMOS集成电路(IC)中实现。LVDS的一个缺点是与PECL相比,其抖动性能降低,但正在研究新技术,以实现与LVPECL相同水平的抖动性能。

LVDS信号输出波形

高速电流转向逻辑(HCSL:High Speed Current Steering Logic)

HCSL 是一种较新的输出标准,类似于 LVPECL。HCSL的一个优点是其高阻抗输出和快速开关时间。建议使用 10 至 30 欧姆串联电阻器,以减少可能的过冲和振铃。其他优势包括最快的开关速度、平均功耗(介于 LVDS 和 LVPECL 之间)以及中等到良好的相位噪声性能。

HCSL信号输出波形

哪种振荡器输出信号类型适合您的需求?

差分与单端

l 正弦波通常提供最佳的相位噪声,其次是CMOS,然后是差分。

l 更高的频率往往需要差分信号。

l 差分信号具有更好的上升和下降时间。

l 差分信号对共模噪声的抵抗力更强。

l 差分信号的EMI(电磁干扰)问题较少。

易用性

LVDS只需要在接收器上设置一个电阻器,而LVPECL需要在发射器和接收端同时端接。

速度最快

LVDS比CMOS更快,HCSL和LVPECL比LVDS速度更快,但可能需要更高的功率。

功耗最低

LVPECL速度更快,但功耗更高,因此我们建议使用CMOS或LVDS来实现低功耗。

抖动性能

如果是从抖动性能来看,LVPECL信号输出是可以获得最佳抖动性能,然后是LVDS,然后是CMOS。