时间:2026-03-13

时间:2026-03-13  来源:

来源:

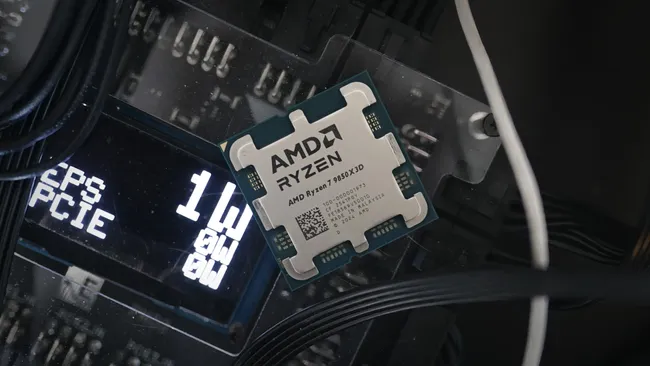

“今年CPU又变得很酷了”在摩根士丹利科技、媒体与电信大会上,David Zinsner形容当前的市场。Lisa Su也给出类似判断:CPU业务需求的增长,已超出预期。

过去几年,AI基础设施的关注点都在GPU上。但随着AI系统规模不断扩大,工程师们逐渐发现一个事实:算力不仅来自芯片本身,还来自整个系统的协同效率。

在一台AI服务器里,CPU负责调度GPU、管理数据流、协调各类计算资源。当训练任务和推理业务持续增长时,这种系统调度者的角色反而变得越来越关键。

而在系统工程层面,还有一个经常被忽视的因素——时间。

AI服务器里的时间基准

一台AI服务器内部通常包含多个计算单元:CPU、GPU、内存控制器、交换芯片以及网络接口。这些模块需要在统一节奏下运行,否则系统协同效率会受到影响。

在高速链路中,例如光模块或PCIe 5.0 / 6.0接口,数据速率已经进入数百Gbps级别。为了维持高速接口的稳定运行,系统需要低噪声参考时钟,常见的参考频率包括:100 MHz,125 MHz,156.25 MHz等等,这些时钟信号为高速SerDes链路提供基础节拍。在实际设计中,参考时钟的相位噪声与抖动行为往往会被纳入整个链路预算。如果时钟抖动较大,高速接口可能出现误码率上升的情况,而在大规模服务器系统中,这类问题往往比较难排查。

主板级时钟:系统运行的基础节拍

除高速接口外,服务器主板上还有基础时钟,例如 25 MHz 或 50 MHz 的 3225 或 2520 贴片有源晶振。它们为 CPU、交换芯片等核心模块提供统一节拍,是整个系统同步的基础。

工程师在设计时,关注频率稳定性、温度变化下的表现,以及批次一致性。服务器长期连续运行,机箱温度会随负载波动,因此时钟器件的稳定性直接影响系统可靠性。

另有低频时钟 32.768 kHz,为RTC模块提供时间基准。日志时间戳在数据中心排查故障时非常关键,一旦时间出现偏差,定位问题会变得困难。

芯片测试设备中的时钟需求

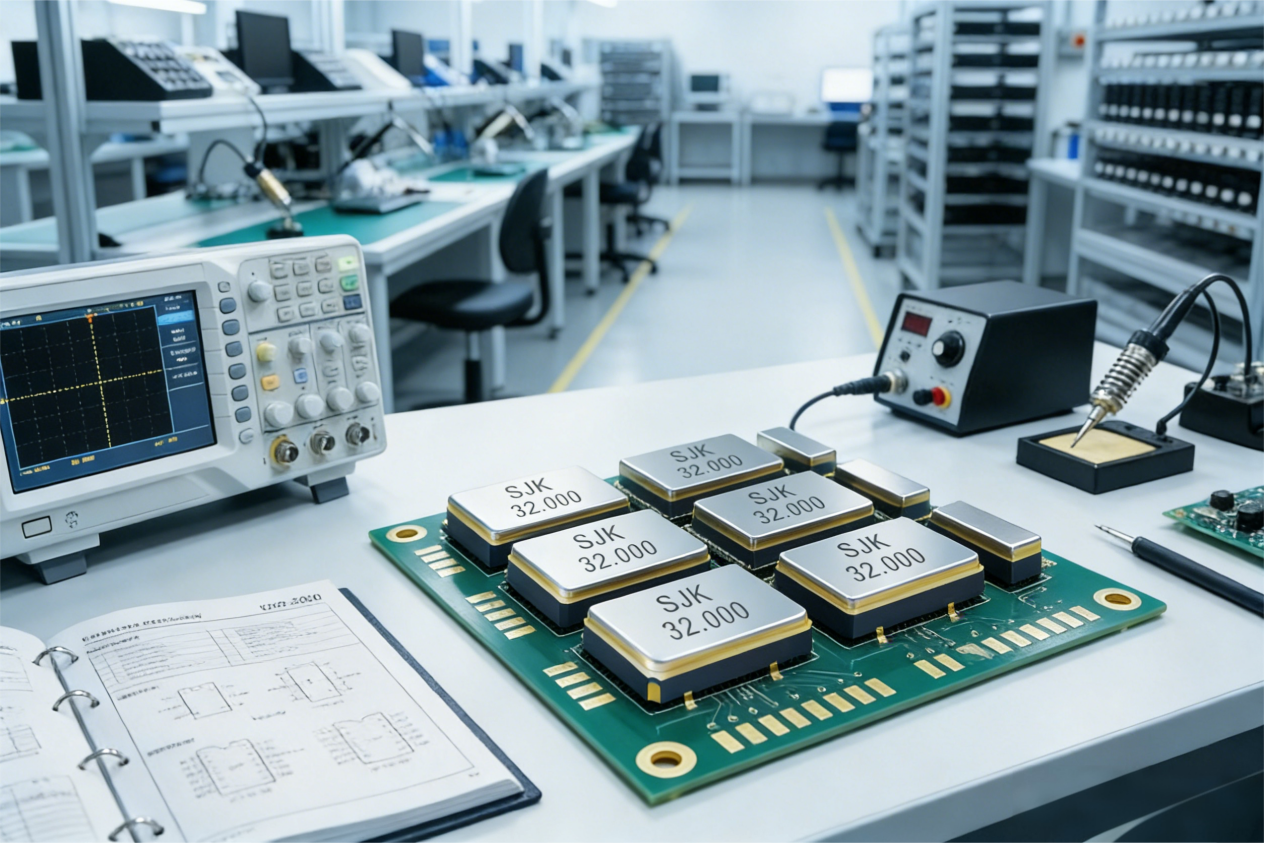

AI芯片需求增长,也推动了芯片测试设备的发展。每颗CPU或GPU在出厂前都需经过复杂测试,而测试设备也依赖稳定的时间基准。

在测试系统中,CPU承担核心计算任务,对参考时钟的稳定性非常敏感。比如厂商在开发新一代CPU测试板卡时,采用SJK晶科鑫 3225封装、50 MHz、18 pF负载电容 的石英晶体谐振器。小体积封装节省PCB空间,频率与负载匹配度高,可为CPU模块提供稳定时序。

测试设备通常长时间满负荷运行,因此工程师更关注器件在温度变化、长期老化及批次一致性上的表现。在服务器和测试设备中,3225与2520封装都是常用规格,在性能与空间之间取得平衡。

算力扩张背后的基础工程

都说CPU又变酷了,但真正让这些算力猛兽保持步调一致的,往往不是耀眼的芯片,而是没人注意的元器件。晶振,就是其中之一。

它藏在主板上、光模块里,也出现在各种测试设备中。个头很小,却承担着给整个系统提供时间节拍。

在一个拥有上千节点的 AI 集群里,调度系统、分布式训练框架、网络同步机制,都需要依赖这个节拍保持一致。一旦时间基准出现偏差,数据节奏就会被打乱,再强的算力也难以真正发挥出来。

对设备厂商来说,问题不仅是性能,还有器件的供应周期与型号延续性。晶振这类基础元器件的可靠性,往往决定着系统能否长期稳定运行。当 AI 基础设施不断扩张,这些曾经不起眼的小器件,反而开始变得关键。