时间:2022-09-20

时间:2022-09-20  来源:SJK晶科鑫

来源:SJK晶科鑫

什么是差分信号

驱动端发送两个大小相等,方向相反的信号,接收端会有一个相减器,比较这两信号的差值,来判断逻辑位是0 或是1,承载差分信号的那一对走线,即称为差分走线,或差动对,这就是差分信号。

差分信号这点跟传统的单端信号不一样。在单端信号中,所谓的正电压或负电压,是跟GND (电位 = 0)比较出来的。

单端信号:单端信号是在一跟导线上传输的与地之间的电平差。

差分信号:即使用两个物理量之间的数值差异来表示一个信号。从严格意义上来讲,所有电压信号都是差分的,因为一个电压只能是相对于另一个电压而言的。

为什么要用差分信号输出的晶振

差分信号的第一个好处是,因为你在控制‘基准’电压,所以能够很容易地识别小信号,具有错误更正效果。

差分信号的第二个主要好处是,它对外部电磁干扰(EMI)是高度免疫的。除了对干扰不大灵敏外,差分信号比单端信号生成的 EMI 还要少。

差分信号提供的第三个好处是,在一个单电源系统,能够从容精确地处理‘双极’信号。

差分晶振,顾名思义,就是输出是差分信号的晶振。差分晶振是指输出差分信号的晶振,通过使用2种相位彼此完全相反的信号,从而消除了共模噪声,从而实现一个更高性能的系统。

差分晶振的选择

选择差分晶振,首先要确认好频率,然后是电压,时钟逻辑类型,封装体积,工作温度以及频率稳定度(精度ppm)。

目前常用的时钟逻辑类型有LVDS,LVPECL,HCSL,CML四种类型。

目前市场主流差分晶振都是6脚贴片封装,常见的尺寸有7050(7.0*5.0mm),5032(5.0*3.2mm) ,3225(3.2*2.5mm),目前有部分晶振工厂有2520(2.5*2.0mm)尺寸的差分晶振,能做的工厂不是很多,所以主流市场还是7050,5032,3225这几类。

| 规格 | LVPECL | LVDS | CML | HCSL |

| VCM | Vcc-1.4V | 1.2V | Vcc-0.2V | 350mV |

| VSWING_SE | 800mV | 350mV | 400mV | 700mV |

| VOH | Vcc-1V | 1.3625V | Vcc | 700mV |

| VOL | Vcc-1.8V | 1.0375V | Vcc-0.400V | 0V |

| Reference | Vcc | GND | Vcc | GND |

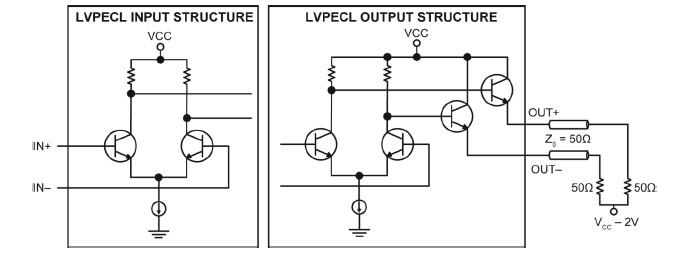

低压,正参考,射极耦合逻辑(LVPECL)源自发射极耦合逻辑(ECL),采用正电源。LVPECL输入是具有高输入阻抗的电流开关差分对。输入共模电压应约为Vcc-1.3V,用于具有内部自偏置或外部偏置的工作余量。

LVPECL信号一个优点是具有清晰尖锐和平衡的信号沿,以及高驱动能力。缺点是功耗相对较高以及有时需要提供单独的终接电压轨。LVPECL技术能实现超过10Gbps的高数据率,为了实现这样高的数据率,必须采用速率极高、边缘陡直(sharp edge)的数据信号,摆幅一般约800mv,也因此它们的功耗超过了LVDS。

LVPECL输出由差分对放大器组成,驱动一对射极跟随器(或开放发射器)。输出射极跟随器应在“有效”区域内工作,始终具有直流电流。OUT +的输出引脚 和OUT-通常连接到差分传输线(Z0 =100Ω)或单端传输线(Z0 =50Ω)用于阻抗匹配,LVPECL输出的正确终端为50Ω至Vcc-2V和OUT + / OUT-通常为Vcc-1.3V,导致近似的直流电流为14mA。

另一种LVPECL输出终止的方法是提供142Ω电阻到GND,为LVPECL输出提供直流偏置,并为GND提供直流电流路径。由于LVPECL输出共模电压为Vcc-1.3V,因此直流偏置电阻可以通过假设直流电流为14mA(R=Vcc-1.3V/14mA)来选择,导致Vcc-3.3V的R=142Ω(150Ω也可以工作)。

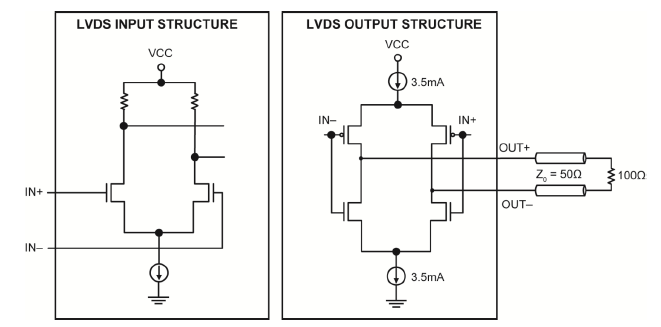

低压差分信号(LVDS)

LVDS信号摆幅低,为350mv,对应功耗很低,速率达到3.125Gbps。总的来说,终接方法简单、功耗和噪声低等优点,使得LVDS成为几十Mbps至3Gbps、甚至更高的应用之首选。

低压差分信号(LVDS)输入需要在IN +和IN-引脚之间连接一个100Ω的电阻,共模电压约为1.2V。如果片内不包含100Ω的端接电阻,则必须包含在印刷电路板(PCB)上。

LVDS输出驱动器由3.5mA电流源组成,通过开关网络连接到差分输出OUT +和OUT-的输出引脚通常连接到差分传输线(Z0=100Ω)或单端传输线 (Z0=50Ω)用于阻抗匹配,通过接收器输入端的100Ω电阻端接导致LVDS逻辑的摆幅为350mV。

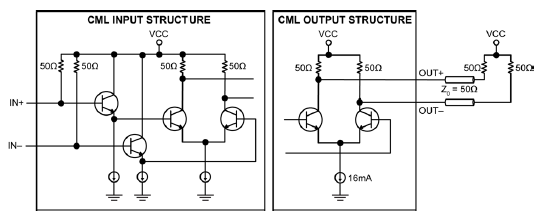

电流模式逻辑(CML)

大多数电流模式逻辑(CML)输入结构都有一个50Ω电阻连接到片内Vcc。如果没有,那么必须在PCB的IN +和IN-的两个输入端上施加一个电压。输入晶体管是射极跟随器,驱动差分对放大器。

CML输出由一对差分共发射极晶体管和50Ω集电极电阻组成。OUT +和OUT-的输出通常连接到差分传输线(Z0=100Ω)或用于阻抗匹配的单端传输线(Z0=50Ω)。通过在共发射极差动BJT中切换电流来提供信号摆幅。假设电流源为16mA(典型值)并且CML输出用一个50Ω电阻上拉到Vcc,这个通过共模电压(Vcc-0.2V),输出电压从Vcc摆动到Vcc-0.4V。

高速电流控制逻辑(HCSL)

高速电流控制逻辑(HCSL)输入要求IN +和IN-的两个输入引脚上的单端摆幅为700mV,共模电压约为350mV。

典型的HCSL驱动器是具有开源输出的差分逻辑。其中每个输出引脚在0和14mA之间切换。当一个输出引脚为低电平(0)时,另一个输出引脚为高电平(驱动14mA)。OUT+引脚和OUT-引脚通常连接到差分传输线(Z0 =100Ω)或单端传输线(Z0 =50Ω),这需要一个外部端接电阻(50Ω到GND),从而为HCSL输入结构提供700mV的摆幅电平。

我司差分晶振产品选择:

普通差分晶振系列:

LV-PECL信号输出:3J(3225)、5J(5032)、7J(7050)

LVDS信号输出:3D(3225)、5D(5032)、7B(7050)

HCSL信号输出:3H(3225)、5H(5032)、7H(7050)

VCXO压控晶振系列

LV-PECL信号输出VCXO:3P(3225)、5P(5032)、7P(7050)

LVDS信号输出VCXO:3V(3225)、5V(5032)、6V(7050)

HCSL信号输出VCXO: 5VH(5032)、7VH(7050)

差分信号输出晶振大部分是应用在高速通信产品行业上,所以输出频率都很高,基本频率范围在10MHz~1500MHz,所有也被叫高频晶振,工作电压大部分在2.5V和3.3V,目前有部分晶振工厂LVDS和HCSL信号输出的工作电压可做到1.8V,意味着有着更低的功率,更加环保。